La macchina produttiva e supply chain dei componenti elettronici

29 giugno 2021

# **Gabriele Braga**

Managing Board ANIE Componenti Elettronici

### Agenda

- Costruire un semiconduttore: ciclo produttivo e materie prime

- Scenario del mercato

- Vulnerabilità e recenti accadimenti

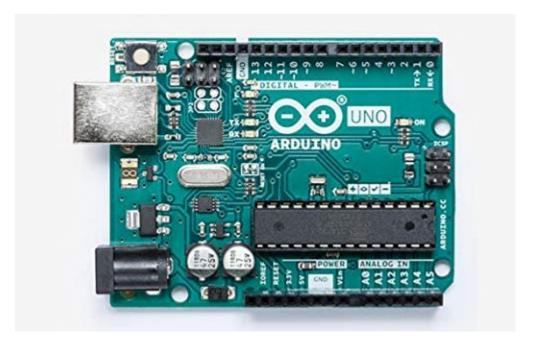

- L'innovazione e la progettazione: il paradosso Lego sull'integrazione e specializzazione

- Autosufficienza: risorse economiche, temporali ed umane

- Proteggersi dalla situazione congiunturale

Costruire un semiconduttore: ciclo produttivo e materie prime

#### Sand

With about 25% (mass) Silicon is – after Oxygen – the second most frequent chemical element in the earth's crust. Sand – especially Quartz - has high percentages of Silicon in the form of Silicon dioxide (SiO<sub>2</sub>) and is the base ingredient for semiconductor manufacturing.

#### Melted Silicon -

scale: wafer level (~300mm / 12 inch)

Silicon is purified in multiple steps to finally reach semiconductor manufacturing quality which is called Electronic Grade Silicon. Electronic Grade Silicon may only have one alien atom every one billion Silicon atoms. In this picture you can see how one big crystal is grown from the purified silicon melt. The resulting mono crystal is called an Ingot.

### Mono-crystal Silicon Ingot – scale: wafer level (~300mm / 12 inch)

An ingot has been produced from Electronic Grade Silicon. One ingot weights about 100 kilograms (=220 pounds) and has a Silicon purity of 99.99999999

#### Ingot Slicing -

scale: wafer level (~300mm / 12 inch)

The Ingot is cut into individual silicon discs

called wafers. The thickness of a wafer is

about 1mm.

#### Wafer -

scale: wafer level (~300mm / 12 inch)

The wafers are polished until they have flawless, mirror-smooth surfaces. Intel buys those manufacturing ready wafers from third party companies. Intel's highly advanced 32nm High-K/Metal Gate process uses wafers with a diameter of 300 millimeter (~12 inches). When Intel first began making chips, the company printed circuits on 2-inch (50mm) wafers. Now the company uses 300mm wafers, resulting in decreased costs per chip.

#### Applying Photo Resist -

scale: wafer level (~300mm / 12 inch)

Fabrication of chips on a wafer consists of hundreds of precisely controlled steps which result in a series of patterned layers of various materials one on top of another. What follows is a sample of the most important steps in this complex process. In this image there's photo resist (blue color) applied, exposed and exposed photo resist is being washed off before the next step (more details later). The remaining photo resist (blue shine on wafer) will protect material that should not get ions implanted.

#### Ion Implantation

scale: wafer level (~300mm / 12 inch)

The wafer is patterned using photolithography (details of how this is done will be described later). The wafer is bombarded with a beam of ions (positively or negatively charged atoms) which embed themselves beneath the surface of the wafer to alter the conductive properties of the silicon in selected locations. The green regions in the image to the right have these implanted alien atoms.

#### Removing Photo Resist -

scale: wafer level (~300mm / 12 inch)

After the ion implantation the photo

resist will be removed and the material

that should have been doped (green)

has alien atoms implanted now (notice

slight variations in color)

#### Applying Photo Resist -

scale: wafer level (~300mm / 12 inch)

The liquid (dark color here) that's

The liquid (dark color here) that's poured onto the wafer while it spins is a photo resist finish similar as the one known from film photography. The wafer spins during this step to allow very thin and even application of this photo resist layer.

#### Exposure -

scale: wafer level (~300mm / 12 inch)

The photo resist finish is exposed to ultra violet (UV) light. The chemical reaction triggered by that process step is similar to what happens to film material in a film camera the moment you press the shutter button. The photo resist finish that's exposed to UV light will become soluble. The exposure is done using masks that act like stencils in this process step. When used with UV light, masks create the various circuit patterns on each layer of the microprocessor. A lens (middle) reduces the mask's image. So what gets printed on the wafer is typically four times smaller linearly than the mask's pattern.

#### Exposure -

scale: transistor level (~50-200nm)

Although usually hundreds of microprocessors are built on a single wafer, this picture story will only focus on a small piece of a microprocessor from now on – on a transistor or parts thereof. A transistor acts as a switch, controlling the flow of electrical current in a computer chip. Intel researchers have developed transistors so small that about 30 million of them could fit on the head of a pin.

Washing off of Photo Resist -

scale: transistor level (~50-200nm)

The gooey photo resist is completely dissolved by a solvent. This reveals a pattern of photo resist made by the mask (dark rectangle here).

#### Etching -

scale: transistor level (~50-200nm)

The photo resist is protecting the high-k dielectric that should not be etched away. Revealed material will be etched away with chemicals.

#### Removing Photo Resist -

scale: transistor level (~50-200nm)

After the etching the photo resist is removed and the desired shape becomes visible.

Polishing scale: transistor level (~50-200nm) The excess material is polished off.

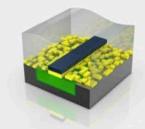

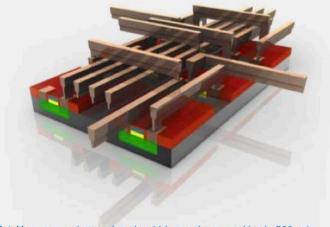

Metal Layers - scale: transistor level (six transistors combined ~500nm)

Multiple metal layers are created to interconnect (think: wires) in between the various transistors. How these connections have to be "wired" is determined by the architecture and design teams that develop the functionality of the respective processor (e.g. Intel® Core™ i5 Processor). While computer chips look extremely flat, they may actually have over 30 layers to form complex circuitry. If you look at a magnified view of a chip, you will see an intricate network of circuit lines and transistors that look like a futuristic, multi-layered highway system.

Wafer Sort Test scale: die level (~10mm / ~0.5 inch)

This fraction of a ready wafer is being put to a first functionality test. In this stage test patterns are fed into every single chip and the response from the chip monitored and compared to "the right answer".

Wafer Slicing -

scale: wafer level (~300mm / 12 inch)

The wafer is cut into pieces (called dies).

The above wafer contains 2nd

generation Intel® Core™ i5 processors

with integrated Intel HD Graphics.

Discarding faulty Dies -

scale: wafer level (~300mm / 12 inch)

The dies that responded with the right

answer to the test pattern will be put

forward for the next step (packaging).

Individual Die -

scale: die level (~10mm / ~0.5 inch)

These are individual dies which have been cut out in the previous step (slicing). The dies shown here are dies of a 2nd generation Intel $^{\circ}$  Core $^{\circ}$  i5 Processor.

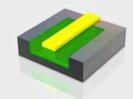

Packaging -

scale: package level (~20mm / ~1 inch)

The substrate, the die and the

heatspreader are put together to form a

completed processor. The green substrate

builds the electrical and mechanical

interface for the processor to interact with

the rest of the PC system. The silver

heatspreader is a thermal interface where

a cooling solution will be put on to. This will

keep the processor cool during operation.

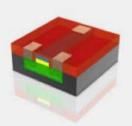

Processor -

scale: package level (~20mm / ~1 inch)

Completed processor (2nd generation

Intel® Core™ i5 Processor in this case). A

microprocessor is the most complex

manufactured product on earth. In fact, it

takes hundreds of steps – only the most

important ones have been visualized in

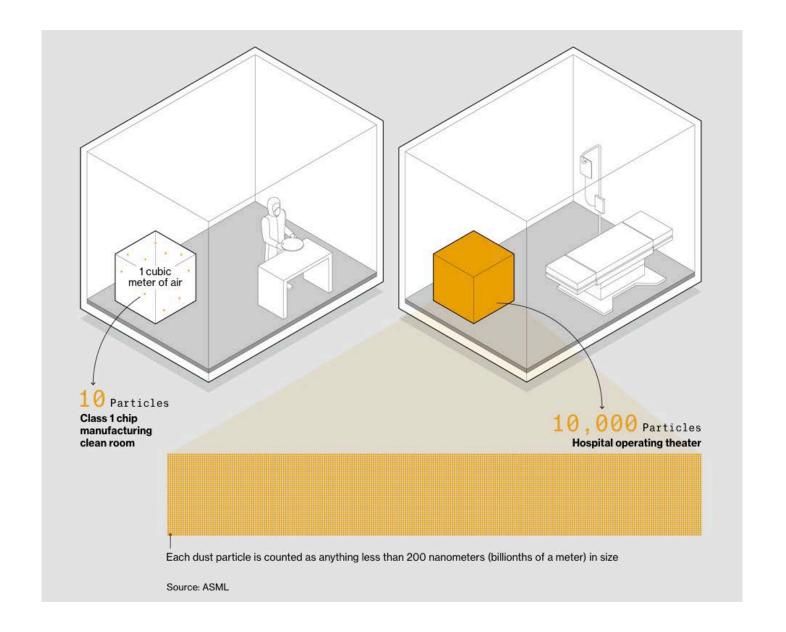

this picture story - in the world's cleanest

environment (a microprocessor fab) to

make microprocessors.

Le materie prime per costruire i semiconduttori

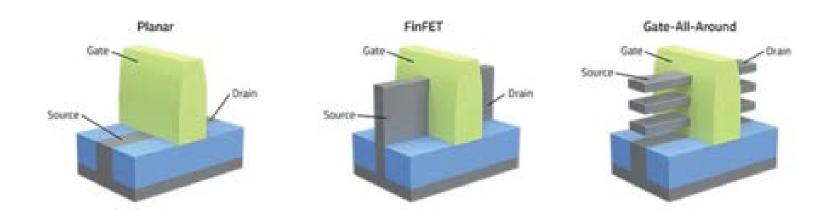

# La metrica del livello tecnologico dei semiconduttori: i nanometri

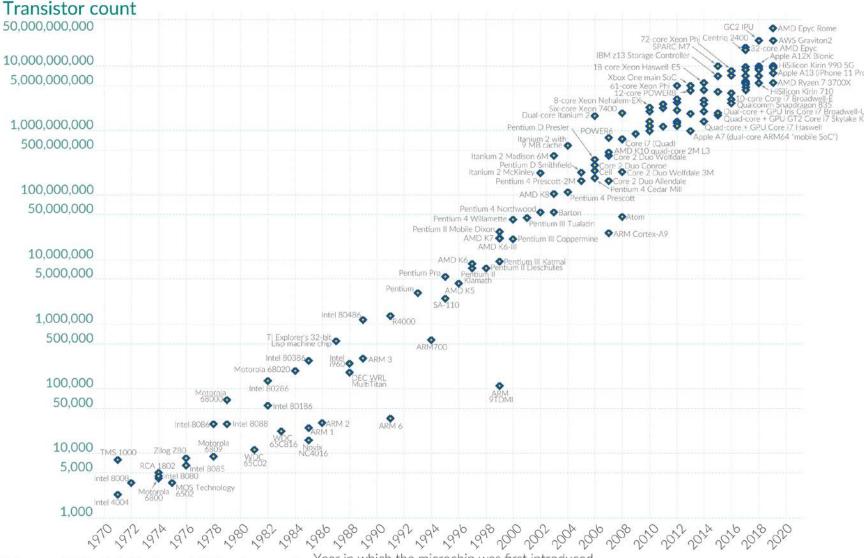

### Moore's Law: The number of transistors on microchips doubles every two years Our World

Moore's law describes the empirical regularity that the number of transistors on integrated circuits doubles approximately every two years. This advancement is important for other aspects of technological progress in computing – such as processing speed or the price of computers.

Year in which the microchip was first introduced Data source: Wikipedia (wikipedia.org/wiki/Transistor\_count)

OurWorldinData.org - Research and data to make progress against the world's largest problems.

Licensed under CC-BY by the authors Hannah Ritchie and Max Roser.

Fig. 2 Number of components per Integrated function for minimum cost per component extrapolated ve time.

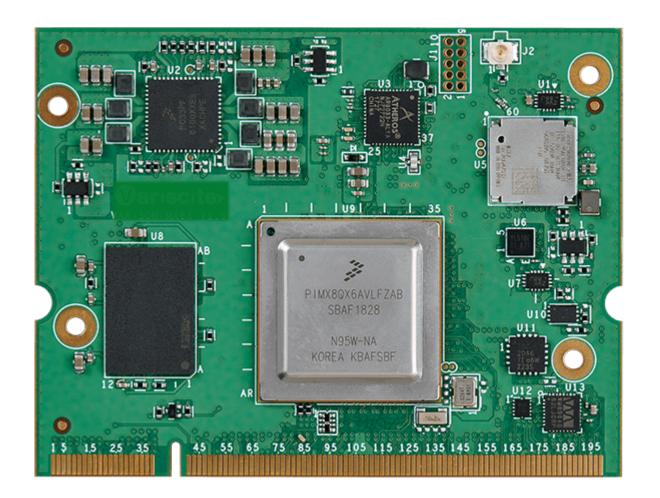

La dinamica evolutiva: l'integrazione

500+

Machines in a fab

Including lithography machines

€15bn+

Cost of building a fab

Average wafer starts per month

1,000+

Steps in chipmaking process

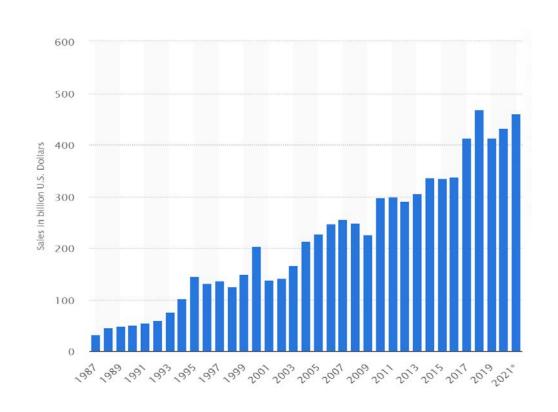

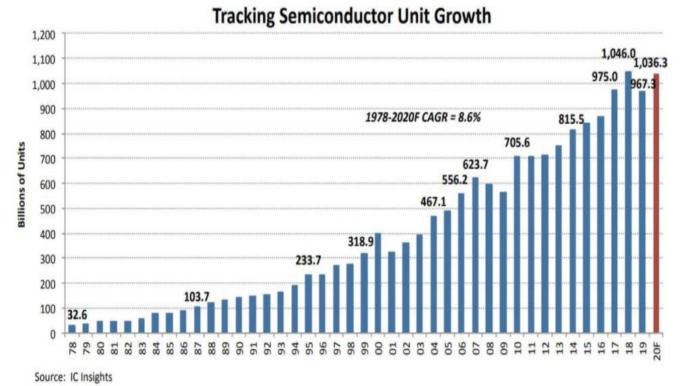

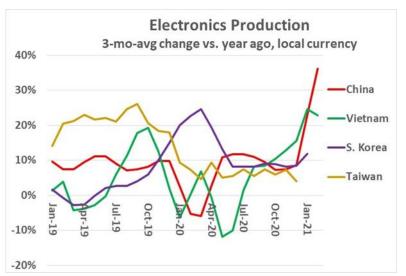

## Scenario del mercato

# Digital transformation as a relentless journey

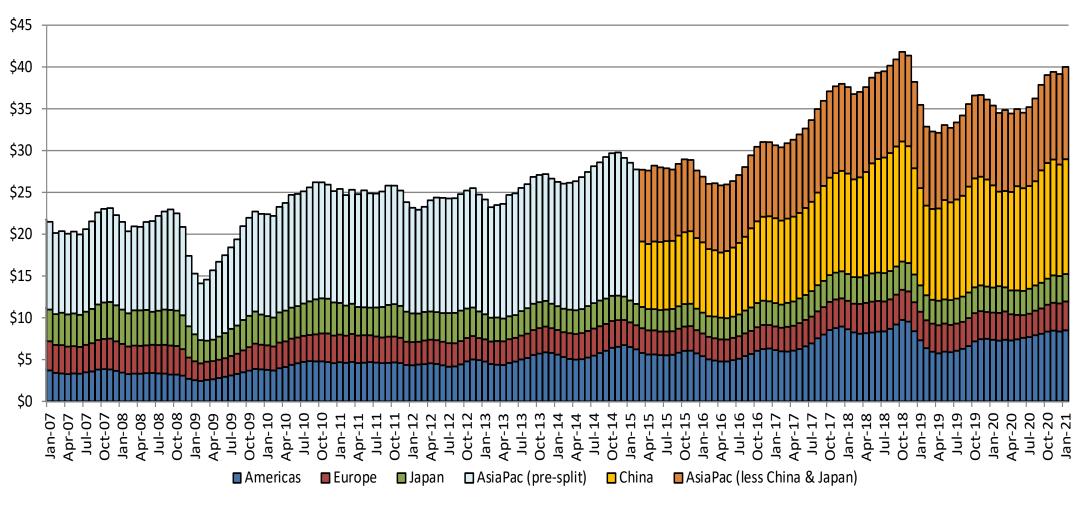

### Monthly Billings Detail by Region

April 2019 was the most recent trough in Worldwide billings, peaking in November 2019. December 2019 through February 2020 were all down M/M. Since March 2020, the Worldwide billings have seen some volatility, January 2021 results up M/M.

Source: Semiconductor Industry Association (SIA) - 3 month rolling average billings

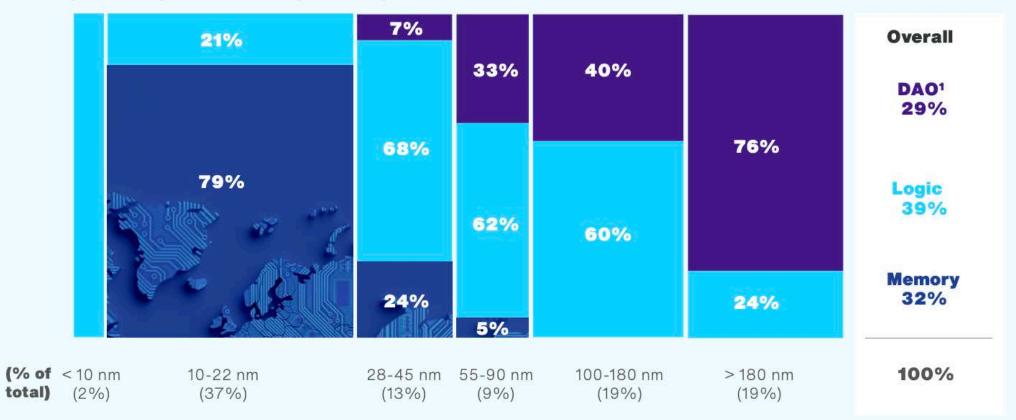

# Tipologia di componenti: geometrie e mercati applicativi

### Global manufacturing capacity by node and semiconductor type, 2019 (% of 8" equivalent wafers per month)

<sup>1.</sup> Discrete, analog and optoelectronics and sensors Sources: BCG analysis based on SEMI data

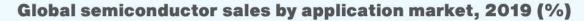

\$412B GLOBAL 2019 SALES

<sup>1.</sup> Discrete, analog and optoelectronics and sensors

<sup>2.</sup> Information and Communications Technology infrastructure, including data centers and communication networks Sources: SIA WSTS, Gartner

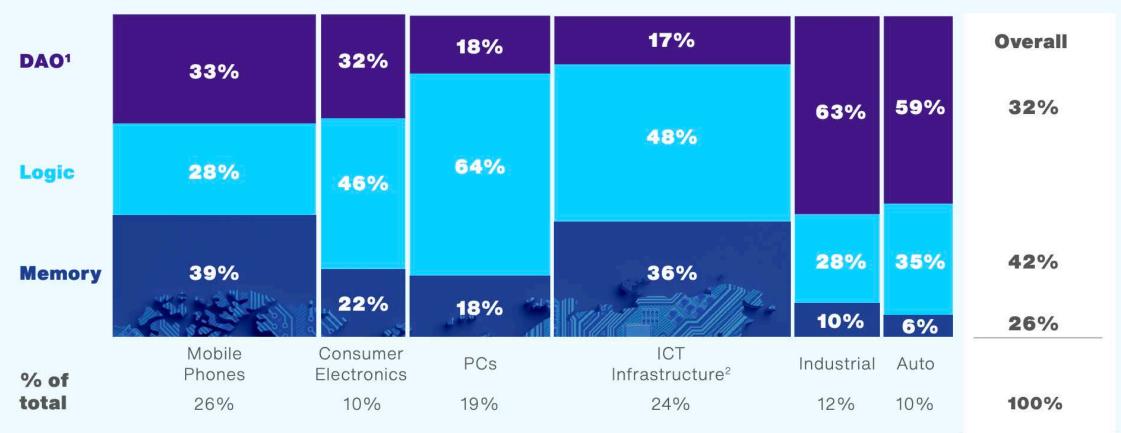

### Alternative views of geographic origin of semiconductor demand

### Global semiconductor sales by geographic area, 2019 (%)

1. Mainland China

Sources: BCG analysis with data from SIA WSTS, Gartner, IDC

# Modelli di business

# Technology complexity and need for scale have led to emergence of business models focused on a specific layer of the value chain

1. Discrete, analog and optoelectronics and sensors Sources: BCG analysis with data from SIA WSTS, Gartner

|                                          |                                             | Design                                   | Manu                                                              | Manufacturing                             |                                                | % OF TOTAL<br>INDUSTRY |                          |

|------------------------------------------|---------------------------------------------|------------------------------------------|-------------------------------------------------------------------|-------------------------------------------|------------------------------------------------|------------------------|--------------------------|

|                                          |                                             |                                          | Front End<br>Wafer fabrication                                    | Back End<br>Assembly & testing            |                                                | Capacity<br>(2019)     | Sales<br>(2019)          |

|                                          |                                             | Company names are illustra               | tive (not exhaustive)                                             |                                           |                                                |                        |                          |

| Integrated Device<br>Manufacturers (IDMs |                                             | I)                                       | Cron TEXAS INSTRUMENTS NXIA ANALOG DEVICES                        |                                           | Memory<br>DAO¹<br>Overall                      | 98%<br>94%<br>67%      | 53%<br>98%<br>75%<br>71% |

| ition                                    | Fabless design                              | Qualcomm DVIDIA  BROADCOM AMD  MEDI/ITEK | IDMs rely on foundries for a portion of their manufacturing needs | IDMs rely<br>on OSATs<br>for a portion of | Logic<br>Memory<br>DAO <sup>1</sup><br>Overall | 79%<br>2%<br>6%<br>33% | 47%<br>2%<br>25%<br>29%  |

| Layer Specialization                     | Foundries                                   |                                          | SAMSUNG SMIC                                                      | their assembly, packaging & testing needs |                                                |                        |                          |

| La                                       | Outsourced<br>Assembly &<br>Testing (OSATs) |                                          |                                                                   | GJCET Powertech Fechnology Inc.           |                                                |                        |                          |

#### IDMs

### Segment economics (% of annual revenue, 2016-2019)

• Gross Margin: 52%

• R&D: 14%

• Capex: 20%

• Operating Cash Flow: 17%

#### **Fabless**

### Segment economics (% of annual revenue, 2016-2019)

| ( 70 Oi aiiiluai levellue, 20            | 10-2010 |

|------------------------------------------|---------|

| <ul> <li>Gross Margin:</li> </ul>        | 50%     |

| • R&D:                                   | 20%     |

| · Capex:                                 | 4%      |

| <ul> <li>Operating Cash Flow:</li> </ul> | 20%     |

#### **Foundries**

#### Segment economics

(% of annual revenue, 2016-2019)

| Gross Margin:                            | 40% |

|------------------------------------------|-----|

| • R&D:                                   | 9%  |

| - Capex:                                 | 34% |

| <ul> <li>Operating Cash Flow:</li> </ul> | 15% |

#### **OSATs**

#### Segment economics (% of annual revenue, 2016-2019)

| ( , , , , , , , , , , , , , , , , , , ,  | ,   |

|------------------------------------------|-----|

| <ul> <li>Gross Margin:</li> </ul>        | 17% |

| • R&D:                                   | 4%  |

| Capex:                                   | 16% |

| <ul> <li>Operating Cash Flow:</li> </ul> | 2%  |

|                                          |     |

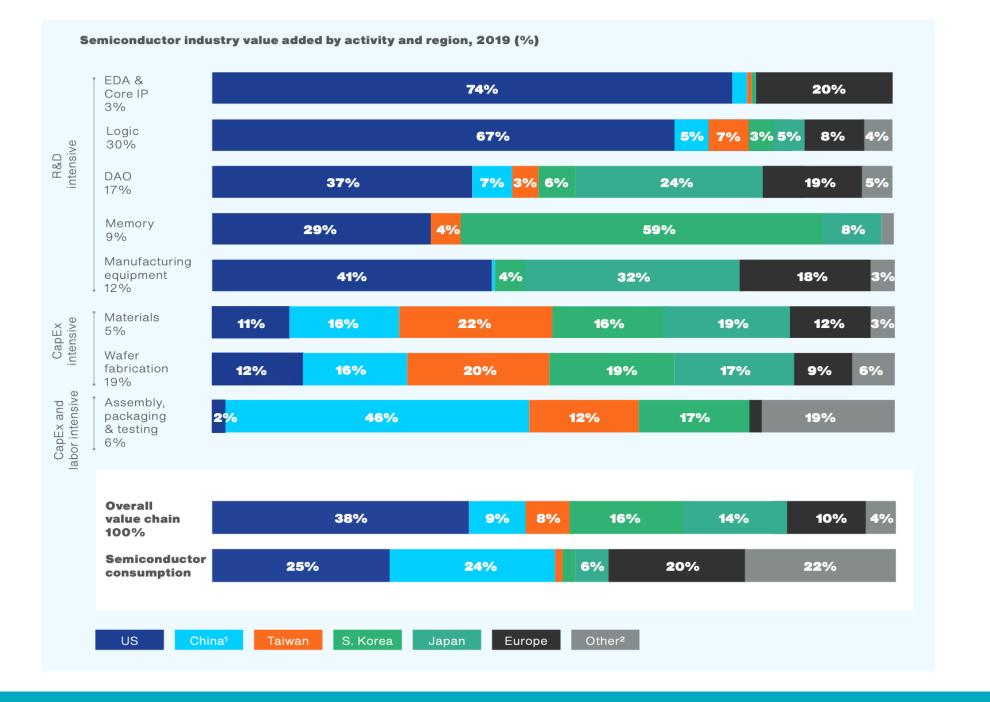

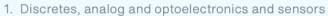

# Regionalizzazione della value chain

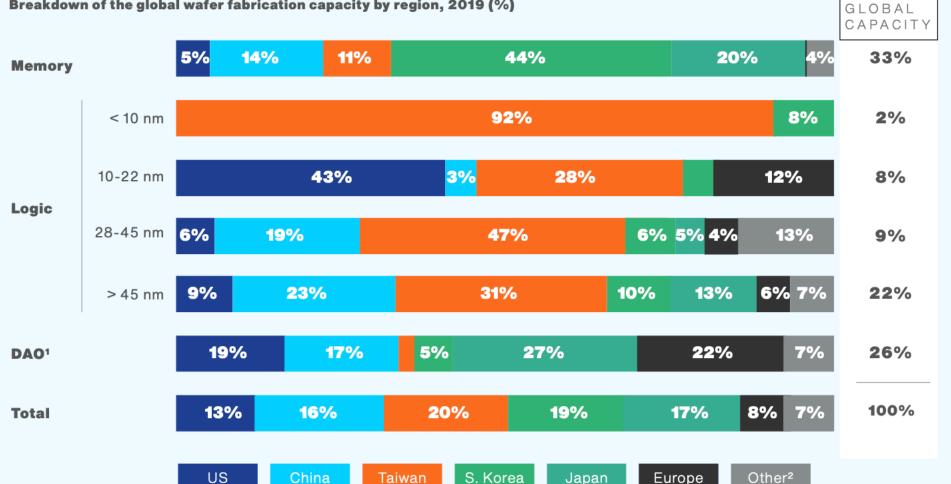

### East Asia + China concentrate about 75% of the wafer fabrication capacity; in particular, all advanced logic capacity < 10nm is currently located in Taiwan and South Korea

Breakdown of the global wafer fabrication capacity by region, 2019 (%)

<sup>2.</sup> Other includes Israel, Singapore and the rest of the world Sources: BCG analysis with data from SEMI fab database

% OF

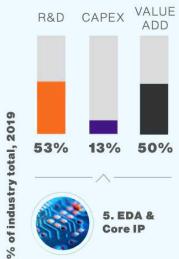

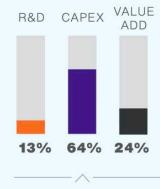

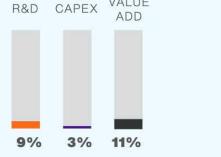

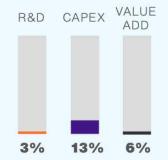

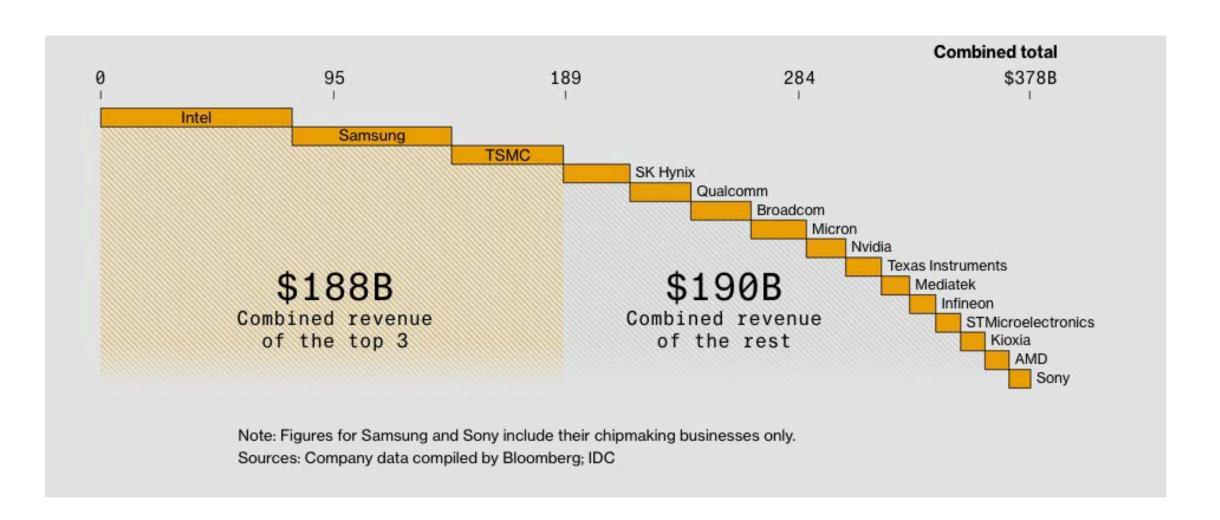

## Produttori e investitori

2. Design

Manufacturing

**3. Front End** Wafer fabrication

**4. Back End**Assembly, packaging & testing

\$412B GLOBAL 2019 SALES

Electronic

**Devices**

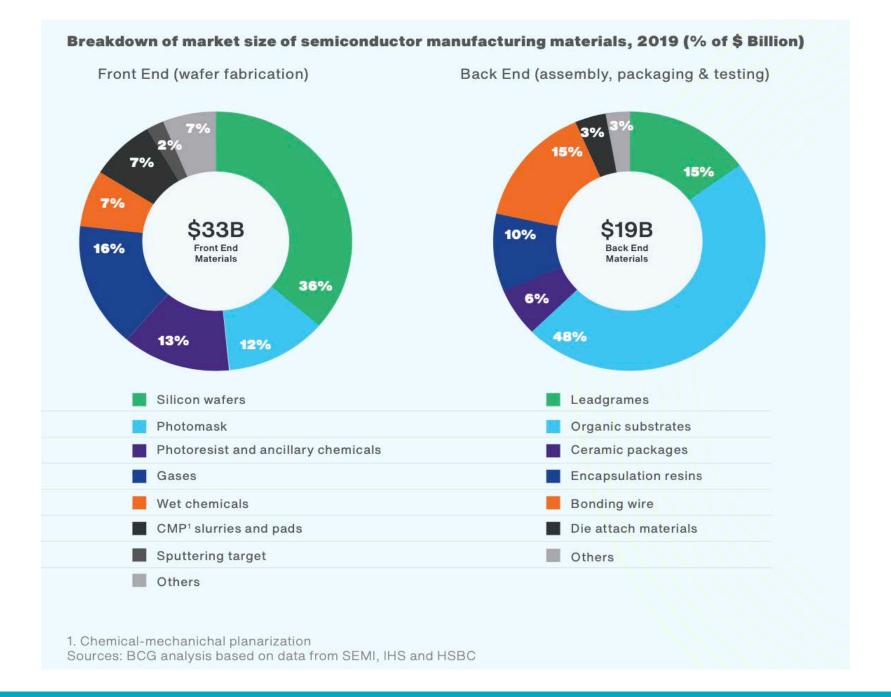

7. Materials

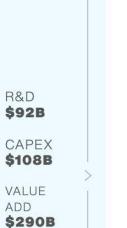

### Breakdown of market size of semiconductor manufacturing equipment by major families, 2019 (\$ Billion)

1. Rapid thermal processing Sources: Gartner

# Lead times for semiconductor production can exceed four months, while switching to a new manufacturer takes a year or longer.

### Semiconductor development and production timelines

|                                      | Capacity buildup                                                                                  |                                            | Product development              |                                                              | Production                                                                                                       |  |

|--------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|

|                                      | New fab<br>buildup                                                                                | Fab<br>ramp                                | Chip<br>design¹                  | Yield and volume ramp-up                                     | Production (cycle time)                                                                                          |  |

| Approximate typical duration, months | 12–18                                                                                             | 6–18                                       | 12–36 <sup>2</sup>               | 6 or more                                                    | 4 or more                                                                                                        |  |

| Influencing<br>factors               | <ul><li>Clean-room<br/>building</li><li>Facilitation<br/>(HVAC, gas,<br/>electric, etc)</li></ul> | •Tool lead times •Hookup and qualification | •Product complexity              | <ul><li>Product complexity</li><li>Fab utilization</li></ul> | <ul><li>Product<br/>complexity</li><li>Physical and<br/>chemical<br/>processes</li><li>Fab utilization</li></ul> |  |

| Other considerations                 |                                                                                                   | Required for expansion of existing plant   |                                  | Required when transferring existing product between fabs     |                                                                                                                  |  |

|                                      |                                                                                                   |                                            | d chip-design<br>run in parallel |                                                              |                                                                                                                  |  |

<sup>&</sup>lt;sup>1</sup>Chip design can be driven independent of fab manufacturing capacity.

<sup>&</sup>lt;sup>2</sup>Eg, ~12-month product lifecycle for mobile phones; 24–36-month development time for automotive microcontroller units. Source: McKinsey analysis

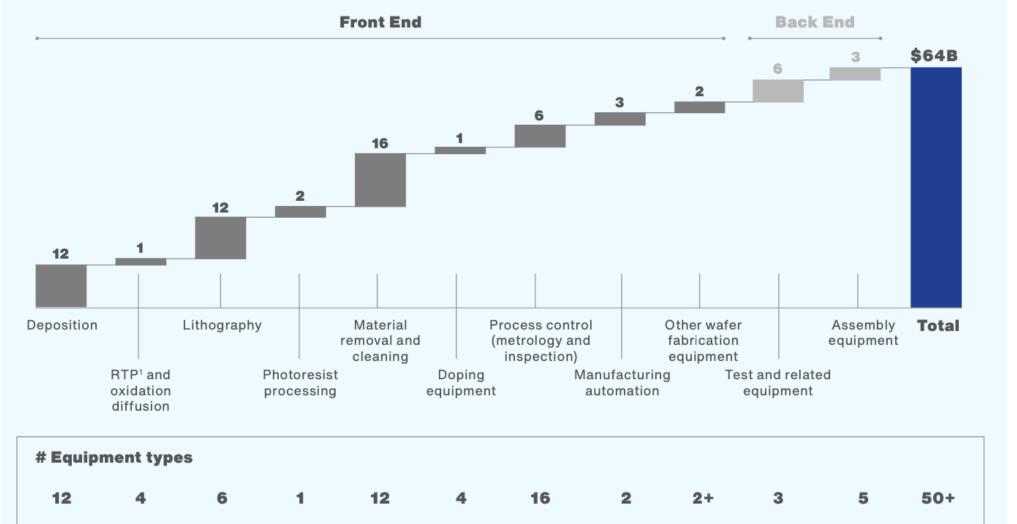

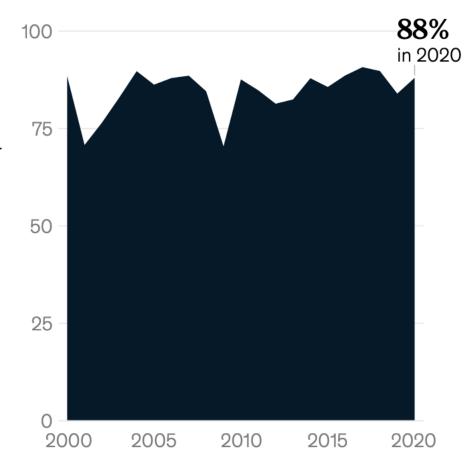

# Over the past two decades, semiconductor capacity increased by an average of 4 percent a year, while utilization has remained high.

# **Semiconductor production capacity,** million square inches per month

# Semiconductor production capacity utilization, %

Source: IHS-Omdia; McKinsey analysis

# OEM - ODM - EMS

| 2020<br>Rank | 2019<br>Rank | Company                    | 2020<br>Revenue | 2020<br>Market<br>Share (%) | 2019<br>Revenue | 2019-2020<br>Growth (%) |

|--------------|--------------|----------------------------|-----------------|-----------------------------|-----------------|-------------------------|

| 1            | 1            | Apple                      | 53,616          | 11.9                        | 43,239          | 24.0                    |

| 2            | 2            | Samsung Electronics        | 36,416          | 8.1                         | 30,247          | 20.4                    |

| 3            | 3            | Huawei                     | 19,086          | 4.2                         | 24,933          | -23.5                   |

| 4            | 4            | Lenovo                     | 18,555          | 4.1                         | 16,773          | 10.6                    |

| 5            | 5            | Dell Technologies          | 16,581          | 3.7                         | 15,584          | 6.4                     |

| 6            | 6            | BBK Electronics            | 13,393          | 3.0                         | 11,653          | 14.9                    |

| 7            | 7            | HP Inc.                    | 10,992          | 2.4                         | 10,729          | 2.4                     |

| 8            | 8            | Xiaomi                     | 8,790           | 2.0                         | 6,974           | 26.0                    |

| 9            | 9            | Hon Hai Precision Industry | 5,730           | 1.3                         | 5,816           | -1.5                    |

| 10           | 10           | Hewlett Packard Enterprise | 5,570           | 1.2                         | 5,561           | 0.2                     |

|              |              | Others                     | 261,109         | 58.0                        | 247,640         | 5.4                     |

|              |              | Total                      | 449,838         | 100.0                       | 419,148         | 7.3                     |

### Vulnerabilità e recenti accadimenti

### The Perfect Storm

- Demand Debounce after downturn

- Relentless Pervasivity

- Raw Material Price Increase

- Earthquakes, Tsunami, Fires

- Inclement Weather

- Transportation Disruption

- Trade Wars and Strategic Investments

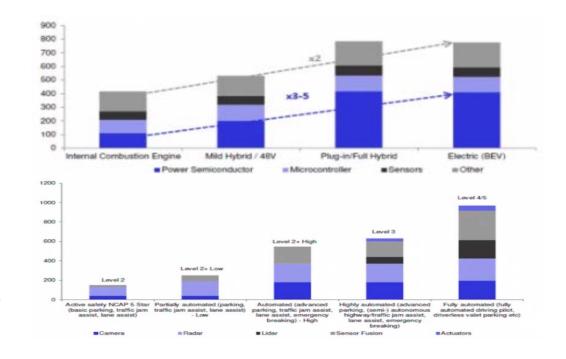

L'innovazione e la progettazione: il paradosso Lego sull'integrazione e specializzazione

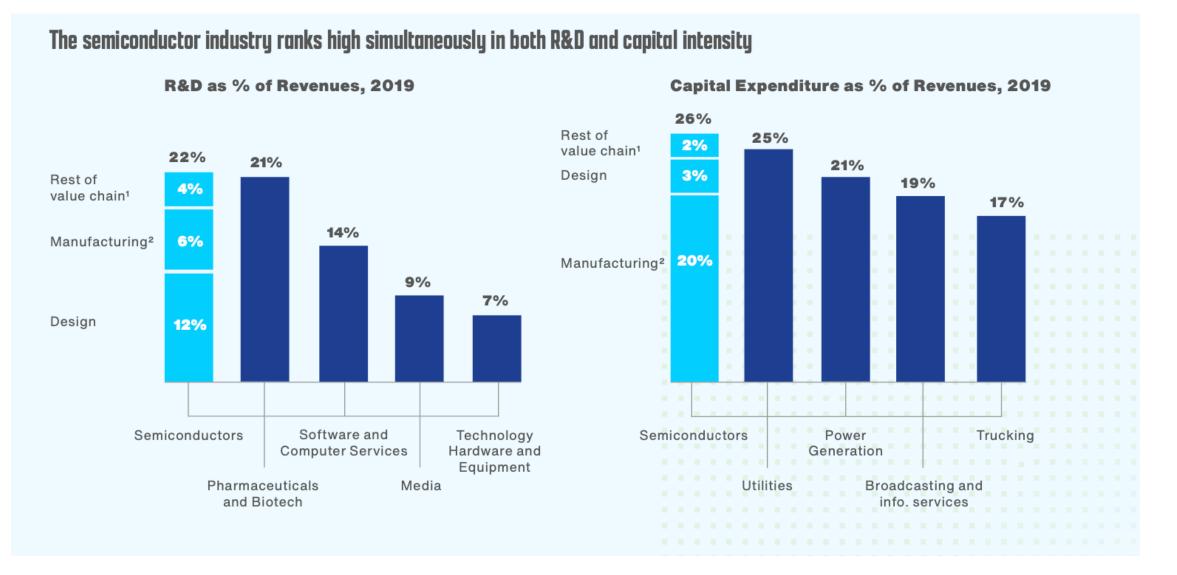

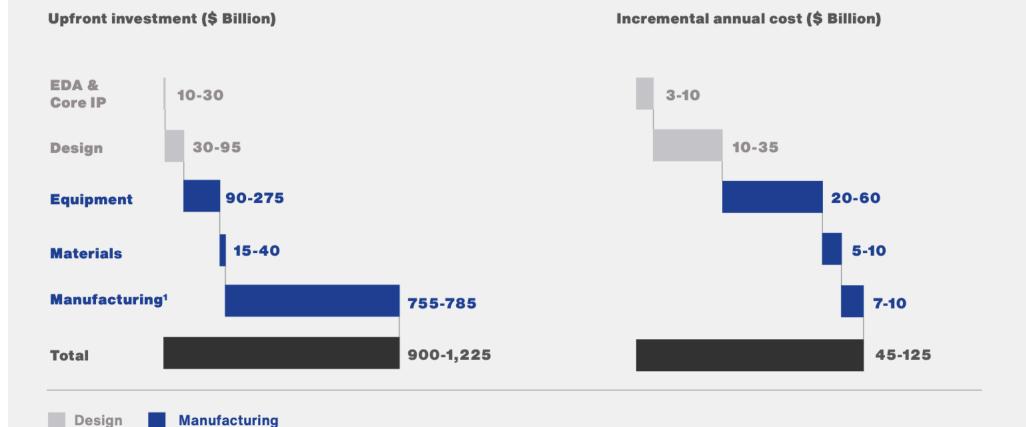

Autosufficienza: risorse economiche, temporali ed umane

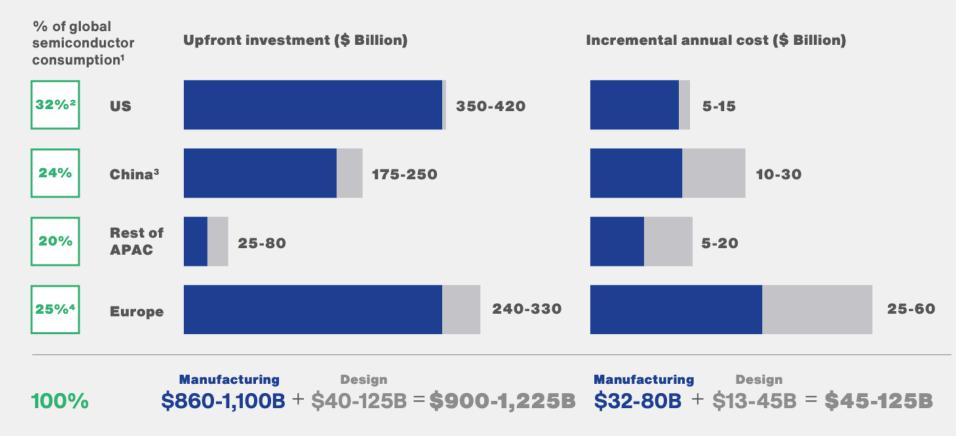

### The staggering cost of hypothetical semiconductor self-sufficiency

<sup>1.</sup> Including both wafer fabrication and assembly, packaging and testing

Note: Range defined primarily by number of local companies assumed to be required to meet the local needs in each activity of the value chain: from just 1 player to supply the entire local market to 3 players typically found in the current global market structure

Sources: BCG analysis

### All regions benefit from the efficiencies of the global semiconductor supply chain

#### Incremental cost to cover 2019 demand with fully "self-sufficient" localized semiconductor supply chains

<sup>1.</sup> Calculated as the estimated semiconductor content in electronic devices sold to end users in each geography in 2019 2. Includes Canada, Latin America 3. Mainland China 4. Includes Middle East and Africa

Note: Range defined primarily by number of local companies assumed to be required to meet the local needs in each activity of the value chain: from just 1 player to supply the entire local market to 3 players typically found in the current global market structure Sources: BCG analysis

# Proteggersi della situazione congiunturale

### Ingegneria dei componenti

- Nel mercato industriale poche aziende hanno volumi rilevanti a livello del singolo part number

- La maggior parte delle produzioni sono «high mix, low volume»

- I criteri di selezione dei componenti hanno effetti sul TCO sul medio e lungo termine (obsolescenza e disponibilità)

- Rinnovare le tecnologie mature con quelle equivalenti più recenti

- Selezionare prodotti industriali a larga diffusione e multipurpose rispetto a prodotti consumer estremamente ottimizzati

- Priorità a package standard rispetto a quelli consumer

- Ottimizzare i volumi per contenere i costi

### Ottimizzazione della Supply Chain

- La partership con il proprio fornitore è strategica

- Estendere il proprio portafoglio ordini per allocare capacità produttiva

- Condividere il rischio: strumenti di gestione del backlog

- Modularizzare il proprio prodotto per ridurre l'impatto della supply chain

- Ridondare i progetti per crearsi delle alternative anche su prodotti proprietari

- Supersets, diebanks, packages

- La situazione potrebbe peggiorare prima di migliorare